## Electronic Design Automation (EDA) Tools and Considerations for Electro-Thermo-Mechanical Co-Design of High Voltage Power Modules

Tristan Evans<sup>1</sup>, Shilpi Mukherjee<sup>2</sup>, Yarui Peng<sup>3</sup>, Alan Mantooth<sup>1</sup> Departments of Electrical Engineering<sup>1</sup>, Microelectronics and Photonics<sup>2</sup>, Computer Science and Computer Engineering<sup>3</sup> University of Arkansas

**College of Engineering** *Mixed-Signal Computer Aided Design Research Lab*

# Outline

- Motivation

- PowerSynth Introduction

- Overview

- Models

- High voltage reliability constraints

- ParaPower Introduction

- EDA tool integration

- Co-design example

- Summary

## Power Electronics is Everywhere

#### **ELECTRIC GENERATION**

## MCPM Co-Design Challenges

# Physical design of multi-chip power modules (MCPM) is time consuming and poses several challenges:

Multi-domain nature of power electronic packaging necessitates consideration of materials and designs towards reduced:

- Electrical parasitics for high performance devices

- Temperature and mechanical stress for higher reliability

- Traditional design flows are iterative and require extensive use of computationally expensive finite element analysis (FEA)

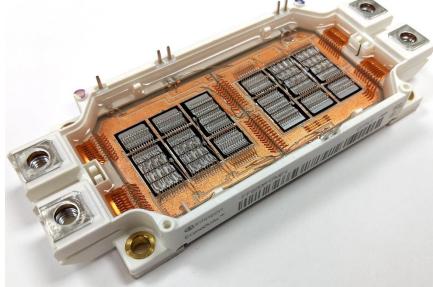

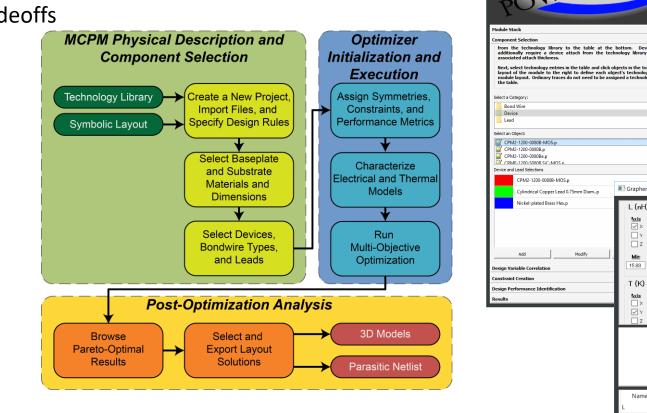

## PowerSynth Overview

E PowerSynth

- 0

- EDA tool for multi-chip power modules (MCPM)

- Multi-objective layout optimization

- Reduced order models

- Pareto-front of tradeoffs

- Design export

Tristan M. Evans, Quang Le, Shilpi Mukherjee, Imam Al Razi, Tom Vrotsos, Yarui Peng, H. Alan Mantooth, "PowerSynth: A Power Module Layout Generation Tool," in *IEEE Transactions on Power Electronics*, vol. 34, no. 6, pp. 5063-5078, June 2019. doi: 10.1109/TPEL.2018.2870346 Highlighted Paper

# PowerSynth Manufacturer Design Kit (MDK) and Technology Library

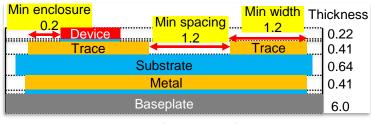

## Layer Stack

- Input file describing layers and technologies

- Holds information pertaining to

- Layer width, length, and thickness

- Layer material properties

# MDK and Design Rules and Checker (DRC)

- Input file containing technologydependent design and processing rules

- Ensures feature sizing and component placement are within processing tolerance

MCPM layer stack

Illustration of design rules pertaining to feature placement and minimum spacing

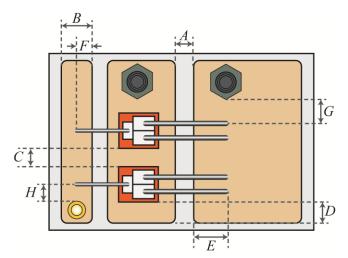

#### PowerSynth technology library wizard

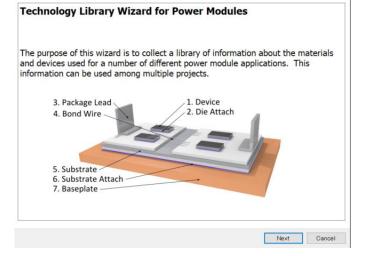

## PowerSynth Layout Engine

- Constraint aware, hierarchical layout engine

- Minimum trace gaps set by trace-to-trace potential difference

- Heterogeneous component support

- Fixed or minimum layout size capabilities

I. Al Razi, Q. Le, H. A. Mantooth, and Y. Peng, "Constraint-Aware Algorithms for Heterogeneous Power Module Layout Synthesis and Reliability Optimization." in 2018 IEEE 6<sup>th</sup> Workshop on Wide Bandgap Power Devices and Applications (WiPDA), 2018, pp. 323-330.

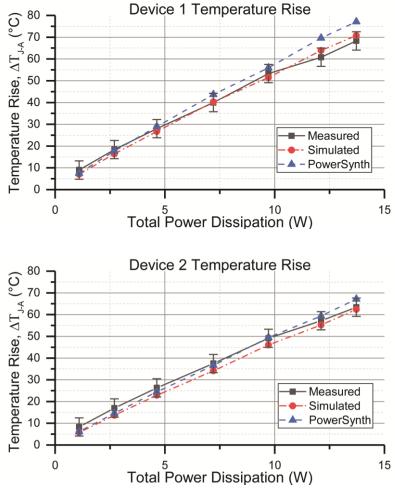

## PowerSynth Thermal Model

#### **Fast Thermal Model**

- Lumped element heat transfer system composed of thermal resistances

- Single FEA sim for characterization

- Includes mutual heating and proximity effects

#### **Device temperature rise results**

- PowerSynth thermal model, Icepak, and thermal camera measurement comparison

- Average error of 4% when compared to simulation or measurement

PowerSynth accuracy within 10% but 8000x faster than FEA

Thermal model validation results for device 1 (above) and device 2 (below) of the test vehicle over a range of power dissipation levels

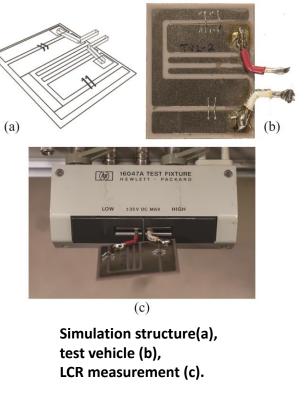

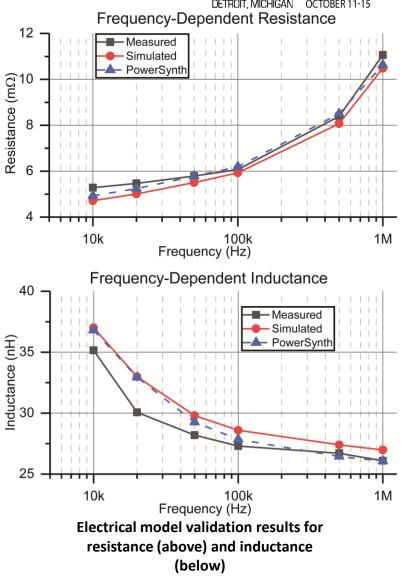

## **PowerSynth Electrical Model**

#### **Response surface model (RSM) for parasitics**

- Based on partial element equivalent circuit method (PEEC)

- Uses FastHenry to run parametric simulations for a given substrate technology

- Maps trace dimensions and vertical separation to resistance and inductance values

#### **Resistance and inductance results**

- Test vehicle layout parasitics compared among PowerSynth, FastHenry, and LCR meter measurement

- PowerSynth model error <10% with both simulation and measurement

RSM parasitics calculation is accurate and up to 6000 times faster than simulation

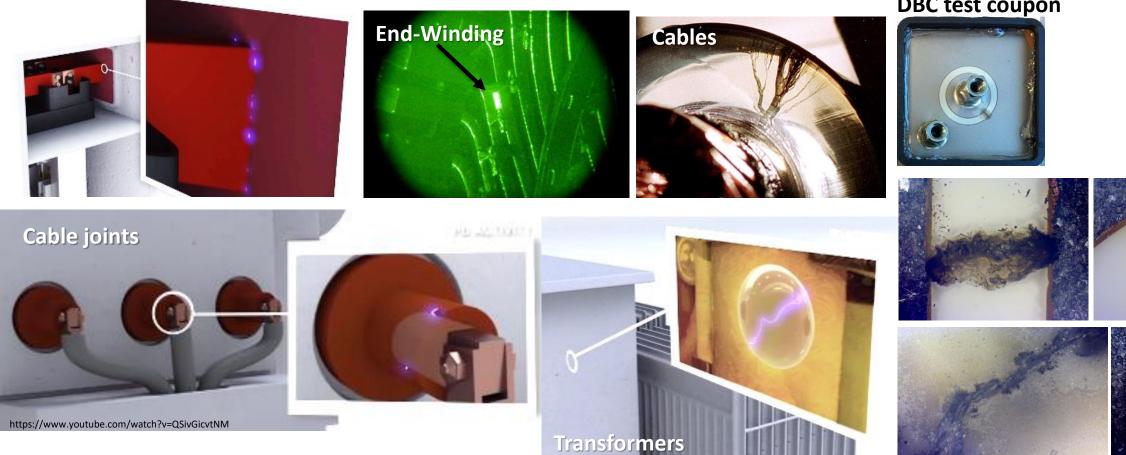

## Partial Discharge (PD) and High Voltage Reliability

**DBC test coupon**

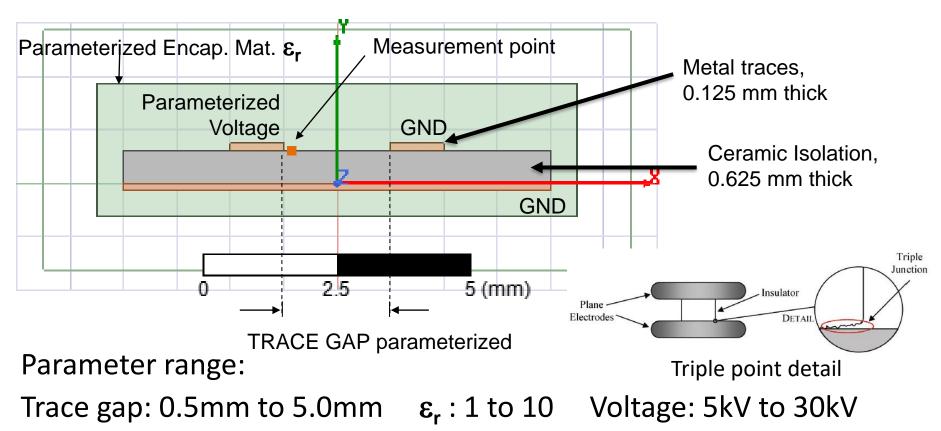

# 2D Electric Field Simulation Setup

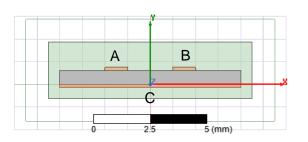

### Model geometry

## **2D Electric Field Simulations**

## Model geometry

Parameter range:

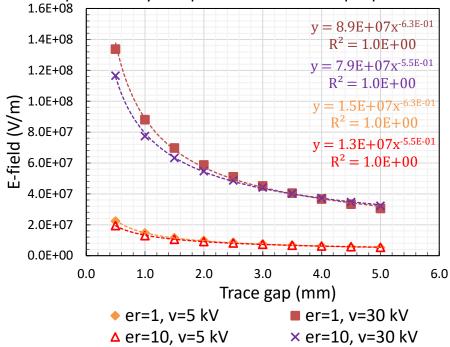

Trace gap: 0.5mm to 5.0mm step size: 0.5mm  $\epsilon_r$ : 1 to 10 step size: 1 Voltage: 5kV to 30kV step size: 5kV

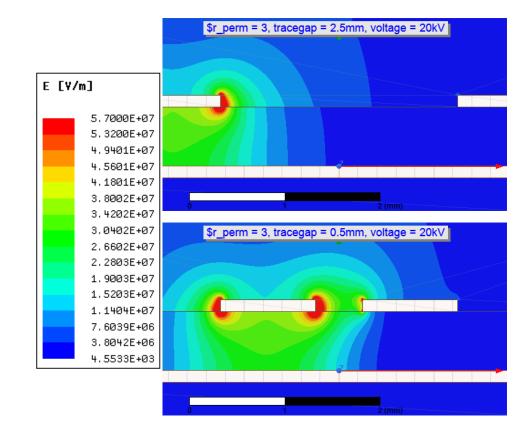

# 2D Electric Field Simulation Results

## General form of equation

### Power curves

$$E = f(v, \varepsilon_r) x^{-g(v, \varepsilon_r)}$$

Where

E is the electric field in kV/mm,

v is the voltage in kV,

x is the gap between traces A and B in mm,

$\varepsilon_r$  is the relative permittivity of the encapsulating material

f and g are functions of v and  $\varepsilon_r$ .

E-field vs. trace gap for corner cases of the parametric sweep of voltage and relative permittivity at a point close to the triple point

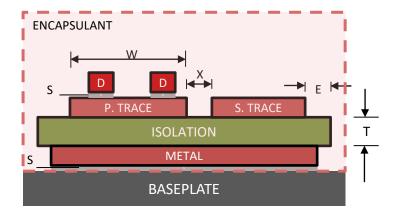

## Implementation in PowerSynth

W: lateral width of trace

- X: lateral trace gap

- E: minimum enclosure

T: vertical thickness of a layer

D: device

P. trace: power trace; S. trace: signal trace

S: substrate attach or die attach

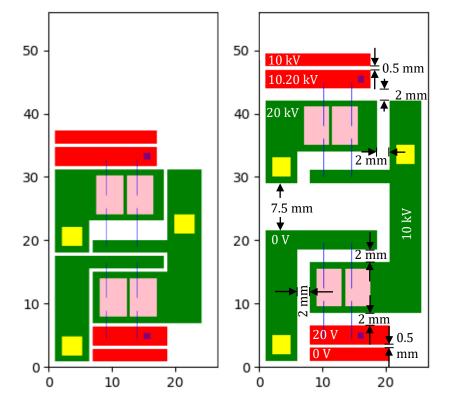

## Default layout vs. Layout with design rules applied

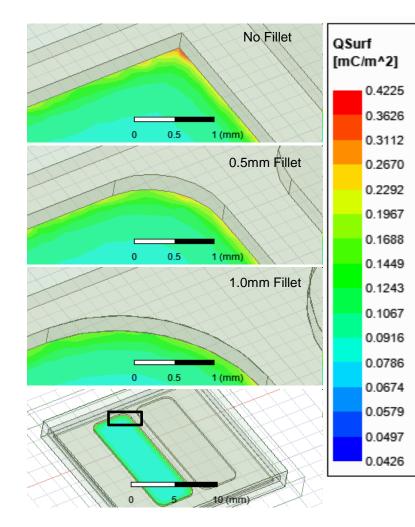

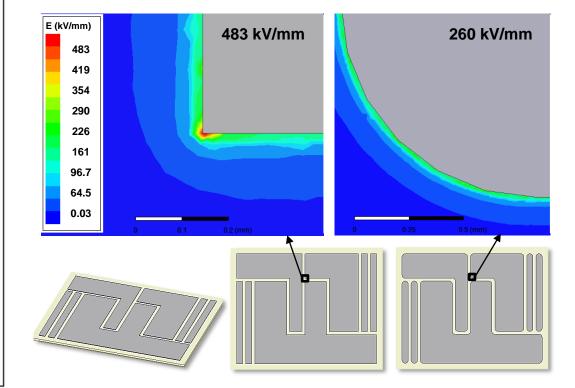

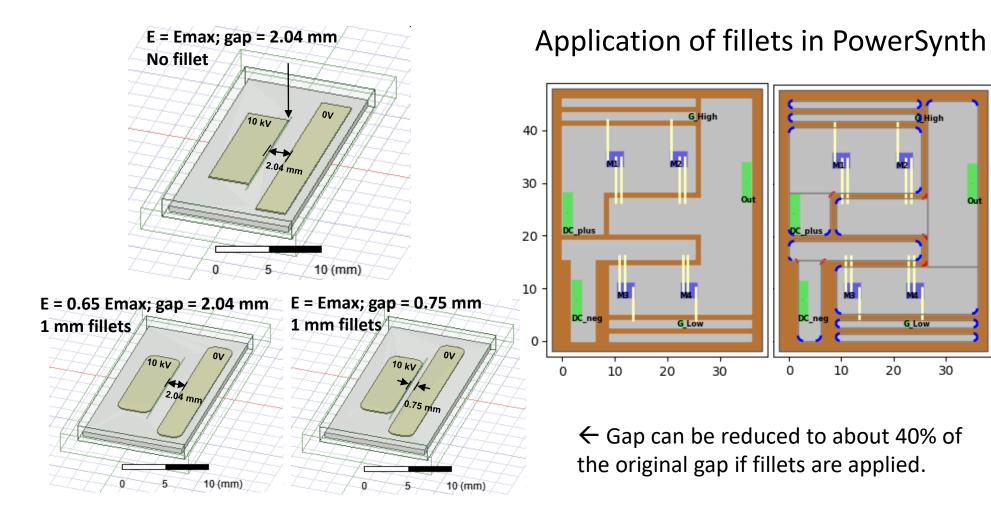

## Effect of Filleting Sharp Corners

E-field and Q<sub>s</sub> are almost halved

# IEEE ENERGY CONVERSION CONGRESS & EXPO

#### **Bottom view** Top view D: Static Structural Equivalent Stress 2 Max stress = 301 MPa Type: Equivalent (von-Mises) Stress Unit: Pa Time: 1 7/15/2020 1:12 PM 3.0092e8 Max 2.7491e8 Max Sharp 2.4889e8 2.2288e8 1.9686e8 1.7085e8 1.4483e8 1.1882e8 0.02 (m) 9.2805e7 0.01 0.02 (m) 0.005 0.015 6.6791e7 Min 0.005 0.015 F: Static Structural\_fillet Equivalent Stress 2 Max stress = 247 MPa; 18% reduction. Type: Equivalent (von-Mises) Stress Unit: Pa Time: 1 Fillet 7/15/2020 1:09 PM 2.4744e8 Max 2.287e8 2.0997e8 1.9123e8 1.7249e8 1.5375e8 1.3501e8 1.1627e8 0.005 0.015 0.02 (m) 9.7536e7 7.8798e7 Min 0.005 0.015

**Filleting Reduces Mechanical Stress**

# Effect of Filleting Sharp Corners with PowerSynth

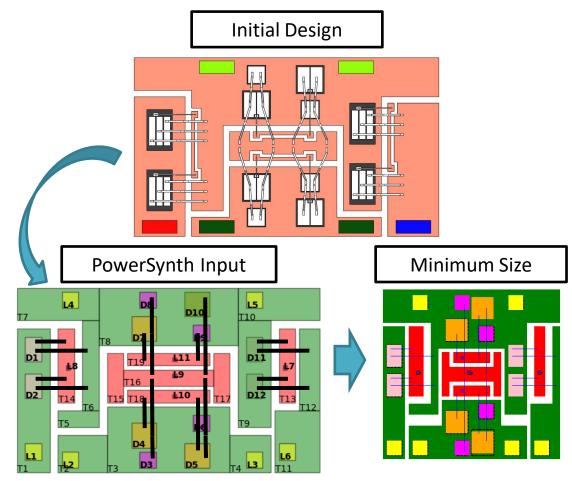

## ParaPower Overview

- Open source co-design tool by US Army Research Lab

- Fast, thermomechanical analysis of power electronics modules

- Parametric analysis tools

- Support for phase change materials

| ARL ParaPower Environmental Parameters |                     |          |                              |                |                                  |               |                  |                                                                             | Initial Temperature (C): 20 |                 |                  |            |                |             |                 |                |

|----------------------------------------|---------------------|----------|------------------------------|----------------|----------------------------------|---------------|------------------|-----------------------------------------------------------------------------|-----------------------------|-----------------|------------------|------------|----------------|-------------|-----------------|----------------|

| ersior                                 | n 0.4.0.0           |          | X- Face                      | X+ Face        | /- Face Y+                       | Face Z- Fa    | ce Z+ Face       | e                                                                           |                             |                 |                  |            |                | · · _       | 20              |                |

|                                        | ,                   |          | h <sup>0</sup>               | 0 0            | 0                                | 100           | 0                |                                                                             |                             |                 | Proc             | ess Temp   | perature (     | <b>C)</b> : | 23              | )              |

| UU                                     | EVCO                | M        | Ta 20                        | 20 20          | ) 20                             | 20            | 20               |                                                                             |                             | 0               | Static           | Analysis   | ۲              | Transi      | ent Analysis    | 5              |

| <u> </u>                               | ARMY RESEARCH       |          |                              |                |                                  |               |                  |                                                                             |                             |                 |                  | Time       | Step (s        | ec):        | 0.1             |                |

| Par                                    | aPowe               | er       |                              |                |                                  |               |                  |                                                                             |                             |                 | N                | lumber of  | Time Ste       | eps:        | 100             | 00             |

|                                        |                     |          |                              |                |                                  |               |                  |                                                                             |                             |                 |                  |            | Total Ti       | me =10      | 00 sec          |                |

| efine                                  | e Features          |          |                              |                |                                  |               |                  |                                                                             |                             |                 |                  |            |                |             |                 |                |

|                                        |                     |          |                              |                |                                  | 10 ( )        | 70 ( )           |                                                                             |                             |                 |                  | 0.010      |                |             | Analy           | sis            |

| -                                      | Dese<br>Basepla     |          | (mm) Y1 (mm)<br>0            | ) Z1 (mm)<br>0 | X2 (mm)<br>60                    | Y2 (mm)<br>60 | Z2 (mm)          | Material<br>Cu v                                                            |                             | Q Typ<br>calar  | >e<br>> 0        | Q (W)      | Num I          | 2           | Loa             | d Profil       |

| 1                                      | SubAtta             |          | 6                            | 4              | 48                               | 53            | 4.2              |                                                                             |                             | calar           | ~ 0              |            | 1              | <u>^</u>    |                 |                |

| 3                                      | SubBac              |          | 6                            | 4.2            | 48                               | 53            | 4.4              |                                                                             |                             | calar           | ~ 0              |            | 1              |             | Sa              | ve Profil      |

| 4                                      | SubCera             |          | 5                            | 4.4            | 50                               | 55            | 5.04             |                                                                             |                             | calar           | ~ 0              |            | 1              |             |                 |                |

| 5                                      | то                  | 11       | 6                            | 5.04           | 49                               | 15.049809     | 5.24             | Cu 🗸                                                                        | s                           | calar           | ~ 0              |            | 1              |             | CI              | ear GUI        |

| 6                                      | 🗌 T1                | 11       | 16.246980                    | 9 5.04         | 49                               | 29.045481     | . 5.24           | Cu v                                                                        | S                           | calar           | ~ 0              |            | 1              | ~           | Pa              | rameter        |

|                                        | <<br>Arrange        | Delet    | e Insert I                   | Move Down      | Move Up                          |               |                  | Material L                                                                  | .ist                        |                 | Up               | odate Mod  | ><br>lel / Vis |             |                 | Help           |

|                                        | Arrange             |          |                              |                | Move Up                          |               | Detailed V       | /isual Res                                                                  |                             |                 |                  |            | lel / Vis      |             |                 |                |

|                                        | Arrange<br>Geometry |          | e Insert I<br>action (Case 1 |                | Move Up<br>Ga<br>Al<br>Cu<br>AlM |               | Tempe<br>"View ( | <b>/isual Res</b><br>erature<br>(3D)" button<br>Time Step C                 | plot:                       | s geor<br>ut: 0 | tress            | f no boxes | lel / Vis      | cked.       | View<br>Pk Plot | (3D)<br>s (2D) |

|                                        | Arrange<br>Geometry |          |                              |                | Ga                               |               | Tempe<br>"View ( | <b>/isual Res</b><br>erature<br>(3D)" button                                | plot:                       | s geor<br>ut: 0 | tress            | f no boxes | lel / Vis      | cked.       |                 | (3D)<br>s (2D) |

|                                        | Geometry            |          |                              |                | Ga<br>Al<br>Cu<br>AlN            |               | Tempe<br>"View ( | <b>/isual Res</b><br>erature<br>(3D)" button<br>Time Step O<br>Time of Inte | plot:                       | s geor<br>ut: 0 | tress<br>netry i | f no boxes | lel / Vis      | cked.       | Pk Plot         | (3D)<br>s (2D) |

| )6                                     | Geometry            | Visualiz |                              | Only)          | Ga<br>Al<br>Cu<br>AlN<br>B       |               | Tempe<br>"View ( | /isual Res<br>erature<br>(3D)" button<br>Time Step C<br>Time of Inte        | plot:                       | s geor<br>ut: 0 | tress<br>netry i | f no boxes | lel / Vis      | Proc.       | Pk Plot         | (3D)<br>s (2D) |

| )6                                     | Geometry            |          |                              | Only)          | Ga<br>Al<br>Cu<br>AlN            |               | Tempe<br>"View ( | <b>/isual Res</b><br>erature<br>(3D)" button<br>Time Step O<br>Time of Inte | plot:                       | s geor<br>ut: 0 | tress<br>netry i | f no boxes | lel / Vis      | Proc.       | Pk Plot         | (3D)<br>s (2D) |

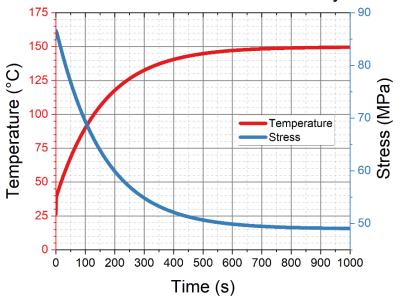

#### Transient Thermo-Mechanical Analysis

##

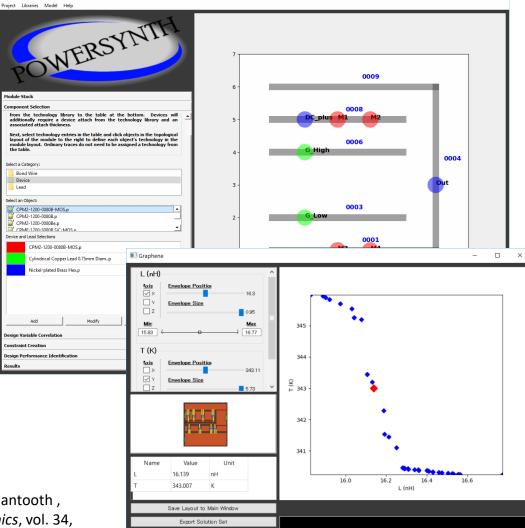

## **API to leverage:**

- PowerSynth layout generation and electrical parasitics extraction

- ParaPower 3D thermo-mechanical analysis

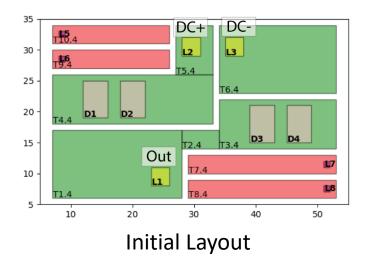

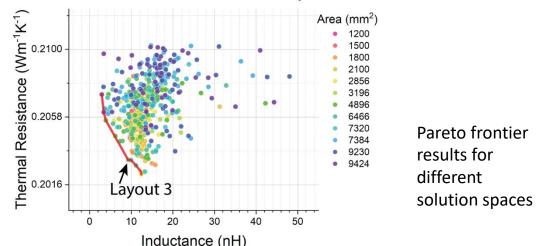

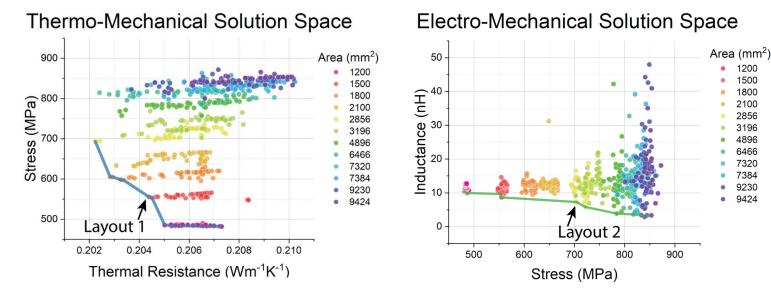

# Co-Design Example (1/2)

- Half bridge layout

- Loop inductance from DC+ to DC-

- 10 W power dissipation/die, 25°C backside temperature

- 230°C process temperature, -40°C minimum ambient temperature

**Electro-Thermal Solution Space**

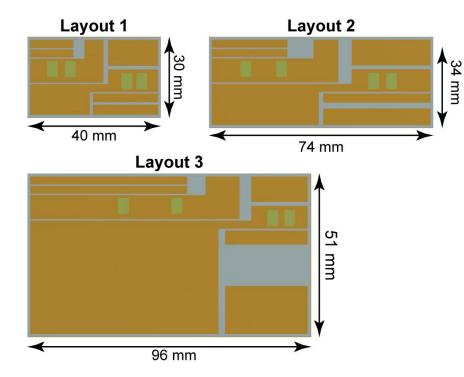

## Co-Design Example (2/2)

### Layouts performance metrics

|          | Dimensions<br>(mm) | Inductance<br>(nH) | R <sub>TH</sub><br>(Wm <sup>-1</sup> K <sup>-1</sup> ) | Stress<br>(MPa) |

|----------|--------------------|--------------------|--------------------------------------------------------|-----------------|

| Layout 1 | 40x30              | 9.93               | 0.204                                                  | 556             |

| Layout 2 | 74x34              | 7.23               | 0.206                                                  | 704             |

| Layout 3 | 96x51              | 9.26               | 0.203                                                  | 816             |

Layouts selected from solution space

# Summary and Future Work

- EDA tools for power electronics gaining momentum

- Integration of PowerSynth and ParaPower enhances capabilities of both

- Layout engine updated with high voltage reliability constraints

- Co-design methods being used to rapidly explore design space tradeoffs

- Continued development:

- Enhance models

- Toward 3D and heterogeneous layout

- Reliability assessment

## Acknowledgements

Power Optimization of Electro Thermal Systems (POETS) An NSF ERC US Army Research Laboratory

Tristan Evans tmevans@uark.edu

Shilpi Mukherjee sxm063@uark.edu

Dr. Yarui Peng yrpeng@uark.edu

Dr. Alan Mantooth mantooth@uark.edu