# Physical Design Automation for High-Density 3D Power Module Layout Synthesis and Optimization

### Imam Al Razi<sup>1</sup>, Quang Le<sup>2</sup>, H. Alan Mantooth<sup>2</sup>, Yarui Peng<sup>1</sup>

<sup>1</sup>Computer Science and Computer Engineering

<sup>2</sup>Electrical Engineering University of Arkansas

UNIVERSITY O

# **Traditional vs. Automatic Design Flow**

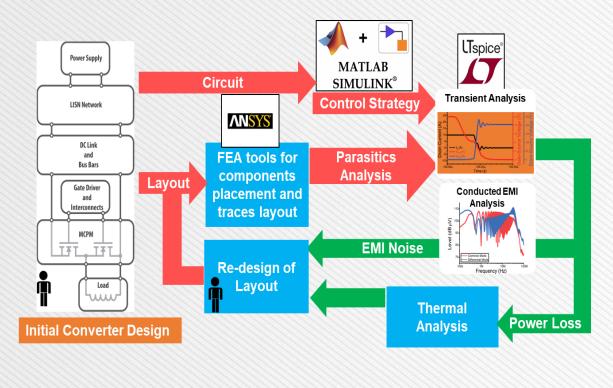

### Manual Design Flow

Tedious and computationally expensive design flow

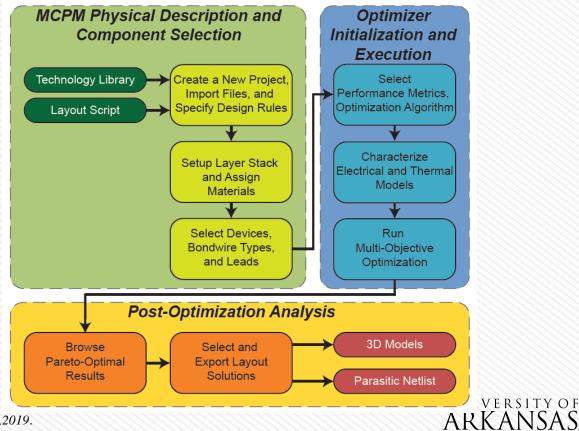

### **Our Approach: PowerSynth**

• A software tool for the layout synthesis and optimization of multi-chip power modules [1].

[1] T. M. Evans et al., "PowerSynth: A Power Module Layout Generation Tool," in IEEE Transactions on Power Electronics, 2019.

Physical Design Automation for High-Density 3D Power Module Layout Synthesis and Optimization

# **PowerSynth 2 Introduction**

### Already demonstrated:

2D and 2.5D heterogeneous power module optimization capability.

## $\hfill\square$ To increase the power density :

3D heterogeneous power modules optimization are obvious.

## **Given Seature Update:**

3D power module layout generation and optimization.

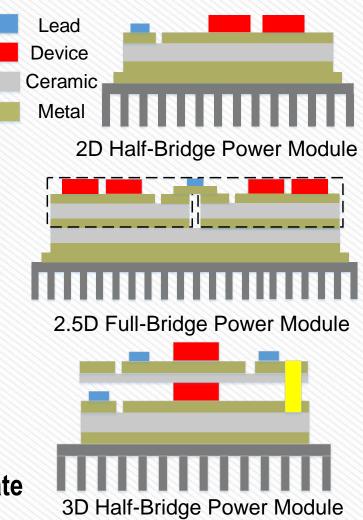

## Three types of layouts handled by PowerSynth:

- 2D layout: One device layer with routing layers on the same substrate

- 2.5D layout: Multiple 2D designs connected on a supporting 2D plane

- 3D layout: Multiple device layers stacked vertically on the same substrate

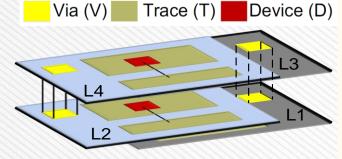

# PowerSynth 2 Methodology

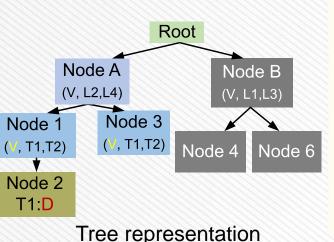

### Layout Representation:

Multiple 2D layers connected with vertical vias

### Data Structure and Algorithms:

Hierarchical tree structure of corner-stitched planes

### □ Layout Generation:

- Hierarchical constraint graphs

- Guarantee DRC-clean solutions

## Layout Optimization:

- Efficient models

- Electrical/thermal/mechanical

- Optimization algorithms

- Tradeoff among multi-objectives

Sample 3D structure

## □ High-level pseudocode:

Read Input Script Create a root node Create group of layers connected with same via

For each group Create a sub-root in the tree containing via location For each layer Create HCS, VCS Create and Evaluate HCG, VCG

For each ancestor from leaf to root Perform bottom-up constraint propagation Evaluate root node and compute available space

For each sub-tree from root to leaf Perform top-down location propagation

#### Evaluate independent nodes

HCS/VCS: Horizontal/Vertical Corner Stitch HCG/VCG: Horizontal/Vertical Constraint Graph

AKKANSA

# **3D Layout Generation Results**

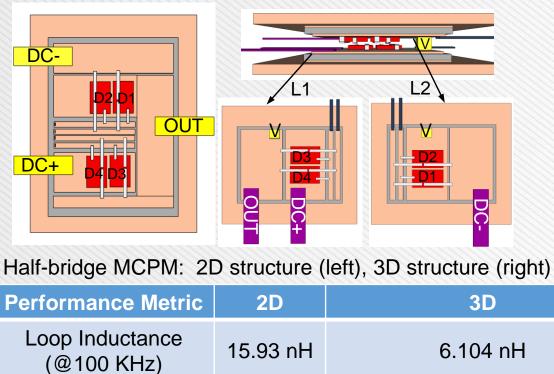

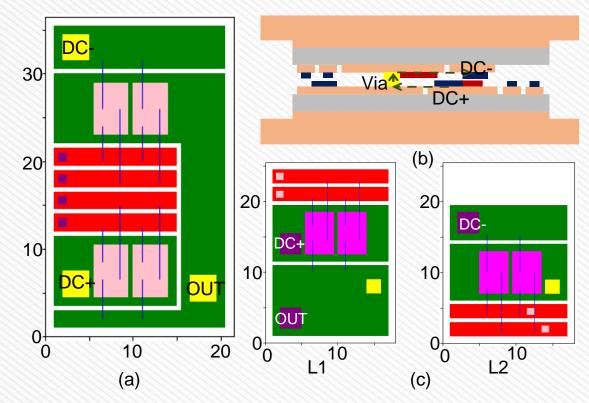

## **2D vs. 3D Performance Comparison:**

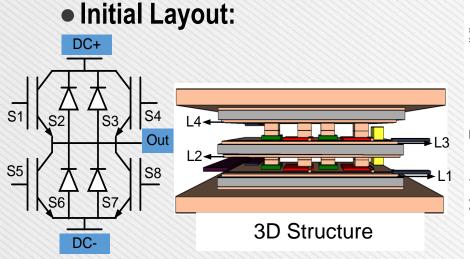

### • Initial layout:

332.15 K

### • Min-sized Result:

(a) 2D layout (b) 3D power loop, (c) high-side (Layer1) and low-side (Layer 2) layers of 3D layout

Max Temperature

370.29 K (single-side cooling)

328.38 K (dual-side cooling)

UNIVERSITY OF

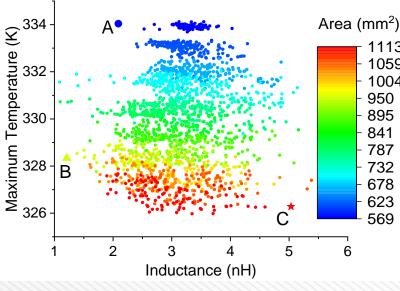

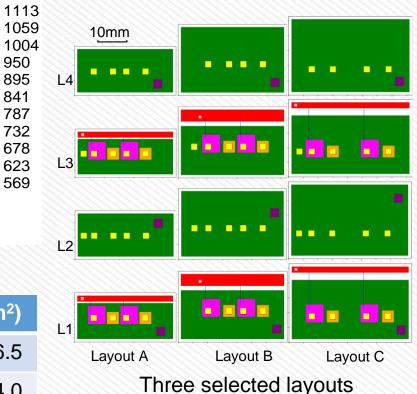

# **3D Layout Optimization Results**

## □ 3D Layout Optimization:

### • Solution Space:

### Electro-thermal evaluation:

- ParaPower [2] thermal model

- FastHenry electrical model

### • Optimization:

- 2400 solutions are generated

- 0.08s per solution generated

[2] "ARL ParaPower" :https://github.com/USArmyResearchLab/ParaPower

| Penormance values |    |        |        |                         |  |  |  |  |  |  |  |  |

|-------------------|----|--------|--------|-------------------------|--|--|--|--|--|--|--|--|

|                   | ID | L (nH) | Т (К)  | Size (mm <sup>2</sup> ) |  |  |  |  |  |  |  |  |

|                   | А  | 1.44   | 334.11 | 34.5 × 16.5             |  |  |  |  |  |  |  |  |

|                   | В  | 1.22   | 328.13 | 37.0 × 24.0             |  |  |  |  |  |  |  |  |

|                   | С  | 2.43   | 324.62 | 42.0 × 26.5             |  |  |  |  |  |  |  |  |

#### Darformanco valuos

UNIVERSITY O ARKANSAS

# **Conclusions and Future Works**

### **Conclusions**:

- Generic and efficient algorithms to handle both intra-layer and inter-layer connections

- Able to handle arbitrary number of layers in an efficient manner.

- This methodology is generic and can be extended towards cabinet-level optimization.

## Future Work:

- Update the algorithm for generic 3D layout cases and validate through measurements.

- Customized optimization algorithm to find a better tradeoff among multiple objectives.

- PowerSynth v2.0 release

| Cabinet                                | 2D/2                                    |                                        |                         |                         |                                   |  |                   |   |                                       |

|----------------------------------------|-----------------------------------------|----------------------------------------|-------------------------|-------------------------|-----------------------------------|--|-------------------|---|---------------------------------------|

| Exp <mark>ort</mark> &<br>Simulation   | Solution<br>Browser                     | Solution<br>Database                   | Netlist<br>Exporting    | Simulation<br>Interface | Expo<br>Functio                   |  | Solution<br>API   |   | EMPro<br>ANSYS                        |

| Optim <mark>iz</mark> ation<br>Toolbox | Genetic<br>Algorithms                   | ctrical Thermal Reliability            |                         |                         | Pre/Post-Layout O<br>Optimization |  | timization<br>API |   | Matlab<br>Scikit-Learn                |

| Layout<br>Evaluation                   | Electrical<br>model                     |                                        |                         | •                       | Partial Discharge<br>model        |  |                   |   | Matlab<br>ParaPower                   |

| Layout<br>Synthesis                    | Constraii<br>(DRC)                      | Constraint Connectivity<br>(DRC) (LVS) |                         |                         | Layout Ge<br>Generation           |  |                   |   | Gmesh<br>Elmer                        |

| Data Input                             | Object-based layout representation      |                                        | MFG Design<br>Kit (MDK) |                         | Embedded scripting<br>environment |  | Material<br>API   |   | ANSYS                                 |

| PowerSynth 2<br>Design Flow            | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |                                        |                         |                         |                                   |  |                   | F | <sup>p</sup> owerSynth 2<br>Libraries |