# PEEC Method and Hierarchical Approach Towards 3D Multichip Power Module (MCPM) Layout Optimization

Quang Le, Tristan Evans, Yarui Peng, H. Alan Mantooth

qmle@uark.edu, mantooth@uark.edu

April 26<sup>th</sup> 2019 Toulouse, France

International Workshop on Integrated Power Packaging (IWIPP 2019)

## Outline

#### I. Overview

- Traditional module design flow

- PowerSynth Introduction

#### **II.** Motivation

- Laplacian Matrix Method

- Limitations

- Mutual Inductance Impact

#### **III. Methodology**

- PEEC overview

- Proposed Methodology

- Coarse discretization

- RLCM evaluation

- Hierarchical Representation

#### **IV. Validation Results**

- Current density validation

- S-parameter extraction for coupling validation

- Loop R, L validation

- Comparisons between models

#### V. Conclusion and future work

- Conclusion and future work

- Acknowledgement

Overview

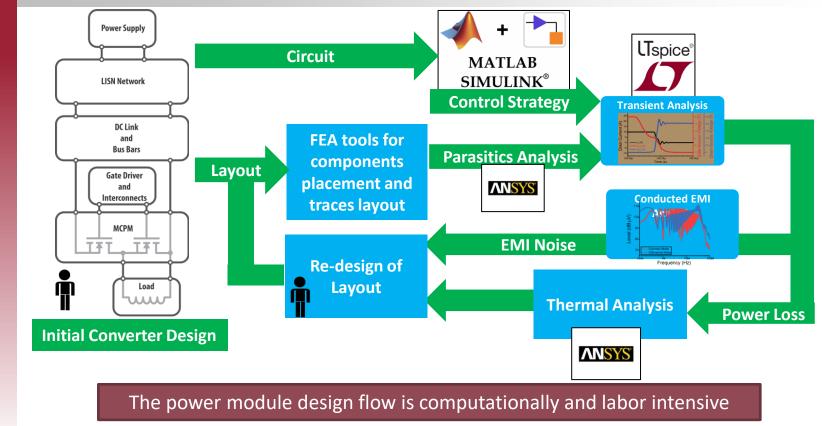

### **Traditional Module Design Flow**

#### Overview Motivation Methodology Results Conclusion

### What Do We Need?

"Imagine we design a circuit without a circuit simulator... How about designing module layout?"

#### We need:

- A more efficient design flow.

- Fast and accurate models for electro-thermal assessment.

- An Electronic Design Automation tool for Power Module design

This would enhance the productivity of the whole design process

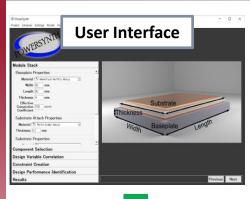

### **PowerSynth Overview**

- Fast and accurate models

- Electrical parasitics

- Fast 2D thermal model

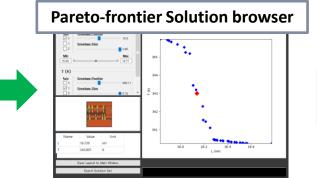

- Design automation through multi-objective optimization

- Quickly explore trade-offs in solution space

- Export to commercial solvers for further analysis

T. M. Evans et al., "PowerSynth: A Power Module Layout Generation Tool," in IEEE Transactions on Power Electronics.

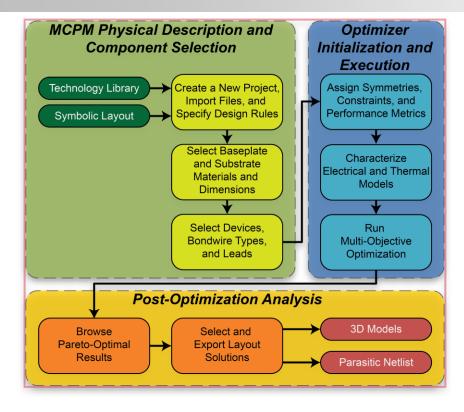

### **PowerSynth Design Flow and Strategy**

Motivation Methodology Results

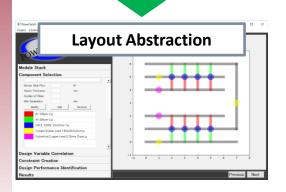

- Fast layout generation to explore the design spaces of integrated power modules

- Fast thermal and electrical analysis to gauge power module performance quickly

- Multi-objective optimization accounts for many trade-off design solutions.

- Easily export layout solution to FEA tools for post-analysis

- PowerSynth Journal Article [1]

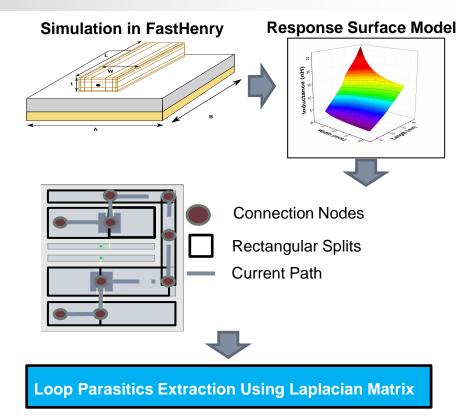

### **Parasitics Extraction in PowerSynth**

#### Overview

Motivation Methodology Results Conclusion

٠

#### **Initial Approach**

- The Laplacian Matrix Method:

- Linear approximation of loop Inductance and Resistance values.

- Fast evaluation and accurate extraction for most 2D layouts

- Response surface for accurate extraction

- Limitations:

- Does not consider mutual inductance between nets.

- No branch current and node voltage information

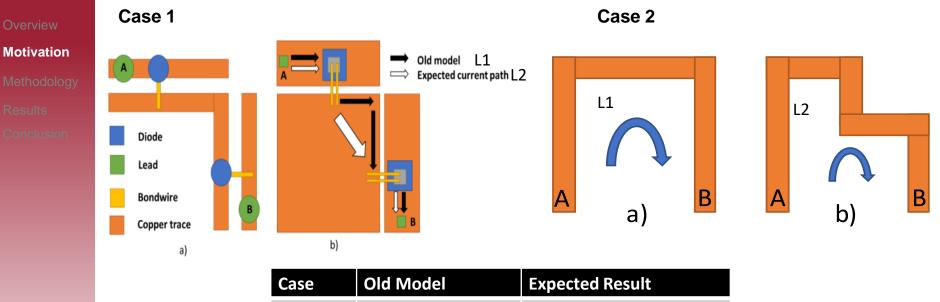

### **Limitations of the Prior Approach**

| Case |                    | LAPECIEU RESUIT    |  |

|------|--------------------|--------------------|--|

| 1    | L1 greater than L2 | L1 less than L2    |  |

| 2    | L1 equal L2        | L1 greater than L2 |  |

|      |                    |                    |  |

The Laplacian matrix can yield good approximation however it fails to compare and contrast between layout cases with these characteristics.

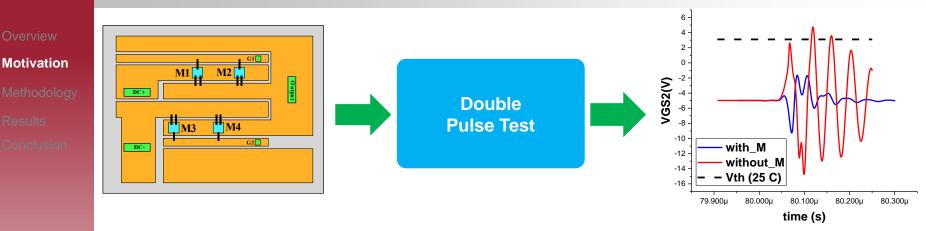

### **Mutual Inductance Impact Case Study**

- Analyze gate signal integrity with and without mutual inductance impact.

- False turn-on voltage in the gate-source signals has been observed in the two cases

- More mutual impact with 3D layout cases

- $\rightarrow$  Crucial to layout automation design

- $\rightarrow$  We can consider most of these issues using PEEC techniques

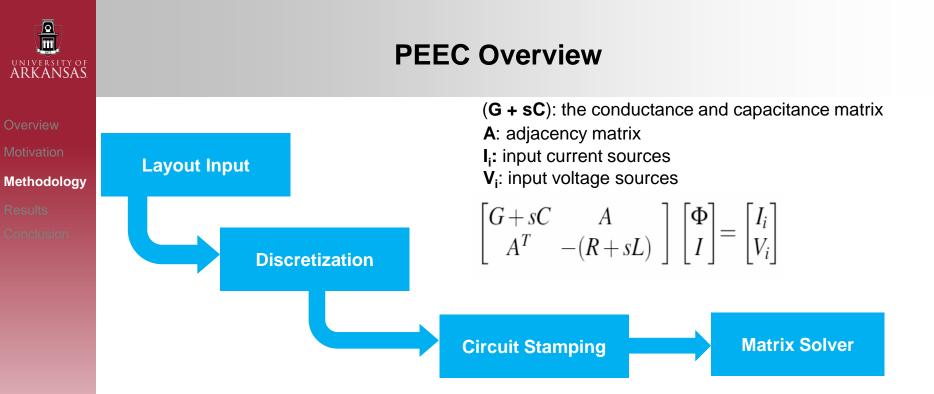

The **P**artial **E**lement **E**quivalent **C**ircuit (PEEC) is a parasitics extraction technique using element stamping and matrix solving.

Methodology

### **PEEC Overview**

#### Solution types:

No Current Solution:

$[(\mathbf{G} + s\mathbf{C}) + \mathbf{A}(\mathbf{R} + s\mathbf{L})\mathbf{A}^{\mathrm{T}}]\Phi = \mathbf{I}_{\mathrm{i}} + \mathbf{A}(\mathbf{R} + s\mathbf{L})^{-1}\mathbf{V}_{\mathrm{i}}]$

No Voltage Solution:

$$[(\mathbf{R} + s\mathbf{L}) + \mathbf{A}^{\mathrm{T}}(\mathbf{G} + s\mathbf{C})^{-1}\mathbf{A}]\mathbf{I} = -\mathbf{V}_{\mathbf{i}} + \mathbf{A}^{\mathrm{T}}(\mathbf{G} + s\mathbf{C})^{-1}\mathbf{I}_{\mathbf{i}}]$$

#### Advantage:

- Can switch between above matrices formations to optimize evaluation time

- Current solution can be used to evaluate electric field and current density inside conductor

- Voltage solution can be used to evaluate electric field between different conductor

#### Disadvantage:

• Increased in computation time due to problem size in MCPM versus the skin-depth

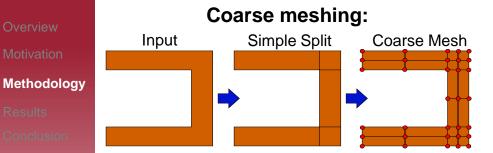

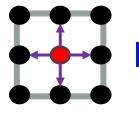

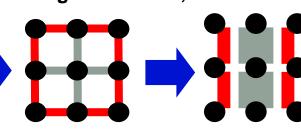

### **Meshing Process**

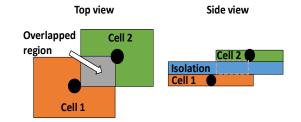

#### Mesh for parasitic capacitance:

Edges and nodes assignment for R, L evaluation:

"A coarse mesh is used in this paper for branch current and node voltage evaluation with less computational effort"

Node Tracking

Edge Formation

Assign Edge Dimension

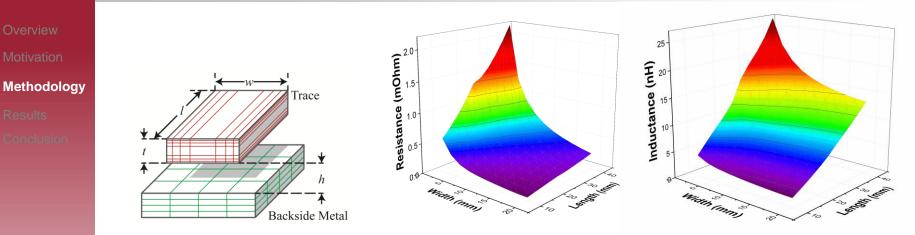

### **RLCM Elements Evaluation**

Meshing structure for response surface

Trace resistance and inductance response surface

Pre-computed model through response surface technique [\*]. These models take input width (W), length (L) of traces and frequency (f).

\* Q. Le, T. Evans, S. Mukherjee, Y. Peng, T. Vrotsos and H. A. Mantooth, "Response surface modeling for parasitic extraction for multi-objective optimization of multi-chip power modules (MCPMs)," 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Albuquerque, NM, 2017, pp. 327-334.

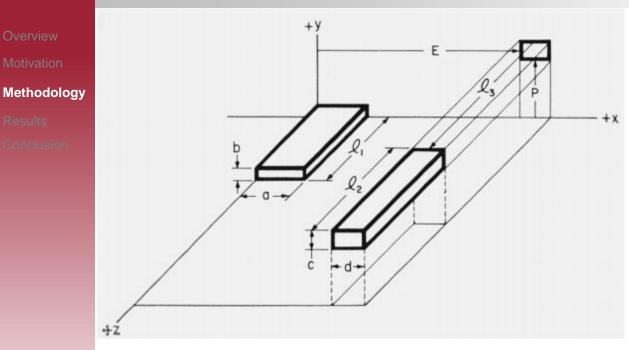

### **RLCM Elements Evaluation**

Exact analytical equation for mutual inductance calculation is used.

Take into account widths, lengths and distances between rectangular bars

C. Hoer and C. Love, "Exact Inductance Equations for Rectangular Conductors with Applications to more Complicated Geometries," J. Res. Natl. Bur. Stand. Sect. C Eng. Instrum., vol. 69C, p. 127, 1965.

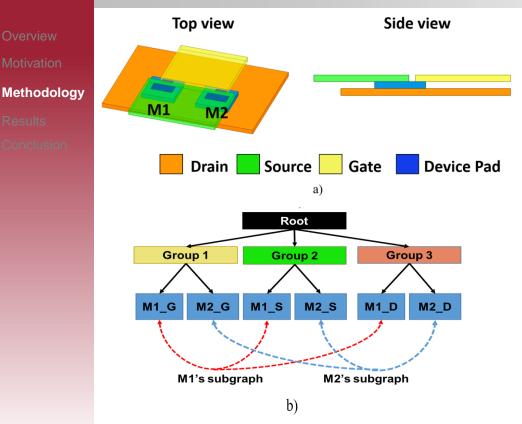

### **Hierarchical Representation**

#### Hierarchical representation:

- Symmetrical designs on same substrate.

- Reduces evaluation time.

- Meshing operation is independent for each group.

#### Components and terminals connections:

- Connections for devices and terminals in each different trace group are represented by a hierarchical tree structure.

- A subgraph is used to represent components internal parasitics (if they exist).

Results

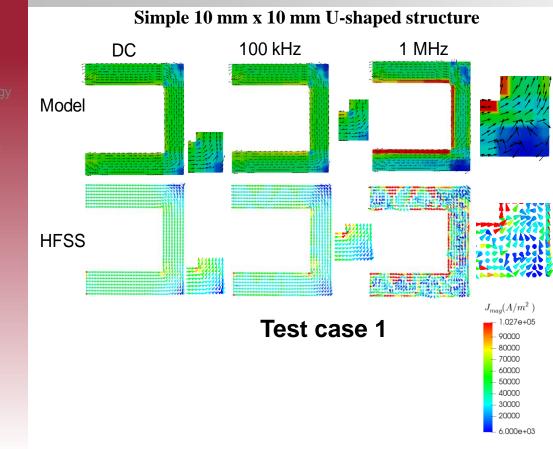

### **Current Density Extraction Results**

#### **Evaluation time comparison**

| Method | Evaluation<br>Time | #Mesh |  |

|--------|--------------------|-------|--|

| Model  | <u>30 ms</u>       | 120   |  |

| HFSS   | 180 s              | 1371  |  |

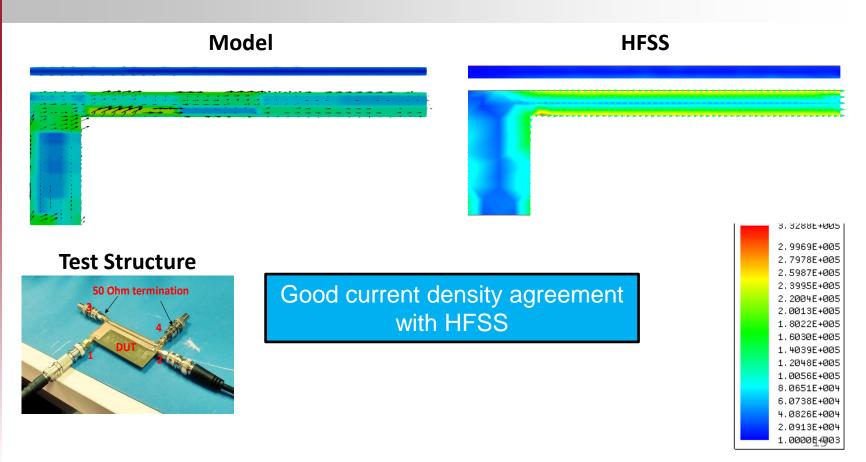

- Current density results are extracted using model and compared with Ansys HFSS.

- Good agreement versus HFSS simulation

Overview Motivation Methodology Results Conclusion

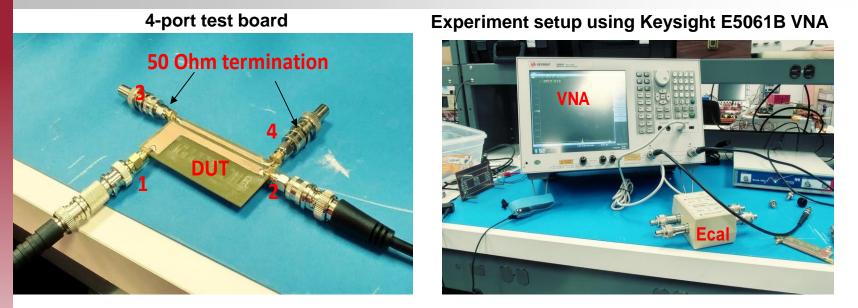

### **Experimental Setup for Coupling Verification**

- Netlist is extracted using model for each selected frequency from 10 kHz 1 GHz

- Synopsys Hspice was used to extract the s-parameter from the netlist

- Same layout is simulated in ANSYS HFSS for validation

#### Test case 2

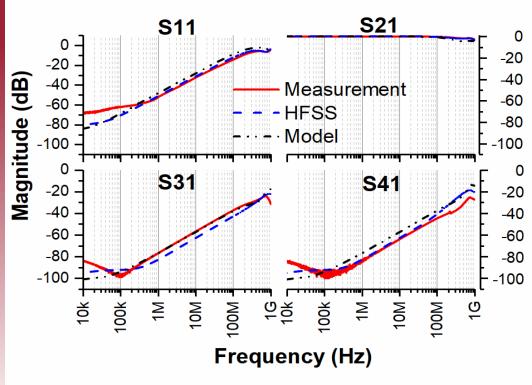

### **Experimental Results for Coupling Verification**

- Measurement results show some noise in the frequency range less than 100 kHz.

- Lower dynamic range at intermediate frequency of 3 kHz

- Contact resistance

between solder and SMA

connector

- Results fit very well in the highfrequency region (>100 kHz).

Overview Motivation Methodology Results Conclusion

### **Current Density Extraction @ 1MHz**

#### Overview Aotivation Aethodology

Results

onclusion

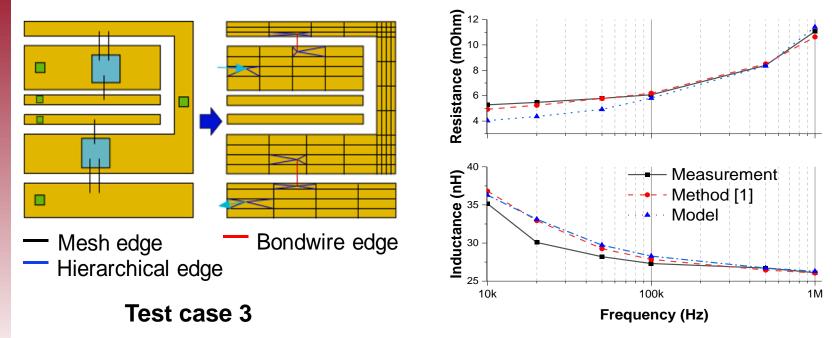

### **Experimental Result for Loop Verification**

#### Layout and Mesh Structure

#### Parasitics Extraction and Measurement Comparison

#### Overview Motivation Methodolog Results

Conclusion

### **Extraction Time Comparison**

|                   | FastHenry | Previous Model [1] | Model without M | Model with M |

|-------------------|-----------|--------------------|-----------------|--------------|

| Extraction Time   | ~300 s    | ~50 ms             | ~180 ms         | ~1.5 s       |

| Speed-up Factor   | 1         | x6000              | x1666           | x200         |

| Mutual Inductance | Yes       | No                 | No              | Yes          |

| I/V Distribution  | No        | No                 | Yes             | Yes          |

Overview Motivation Methodology Results Conclusion

- Accurate model considering mutual coupling and I,V information during optimization.

- Validation through S-parameter measurement.

#### **Conclusion and Future Work**

- Validation for 3D layout.

- Combine with layout engine and optimization engine for layout optimization.

- EMI mitigation model

#### References

Bindra and A. Mantooth, "Modern Tool Limitations in Design Automation: Advancing Automation in Design Tools is Gathering Momentum," in *IEEE Power Electronics Magazine*, vol. 6, no. 1, pp. 28-33, March 2019.

T. M. Evans *et al.*, "PowerSynth: A Power Module Layout Generation Tool," in *IEEE Transactions on Power Electronics*.

Q. Le, T. Evans, S. Mukherjee, Y. Peng, T. Vrotsos and H. A. Mantooth, "Response surface modeling for parasitic extraction for multi-objective optimization of multi-chip power modules (MCPMs)," *2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA)*, Albuquerque, NM, 2017, pp. 327-334.

C. Hoer and C. Love, "Exact Inductance Equations for Rectangular Conductors with Applications to more Complicated Geometries," *J. Res. Natl. Bur. Stand. Sect. C Eng. Instrum.*, vol. 69C, p. 127, 1965

# Acknowledgement

Thank you for your attention !

### Merci de votre attention!